Floating Point Adder

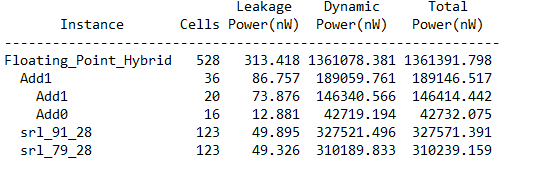

Power Efficient VLSI Design

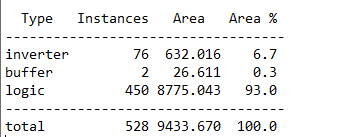

Optimizing mantissa addition in IEEE 754 single precision format using a hybrid RCA-CLA approach for reduced power and area.

Power Efficient

Area Optimized

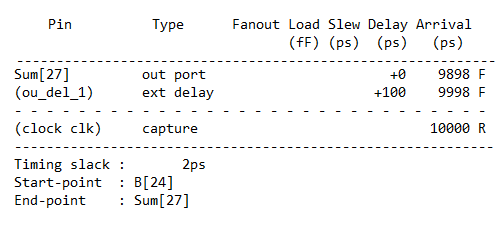

Low Delay

Design Process

Step-by-step IEEE 754 implementation

Architecture & Results

Block diagrams and performance analysis

Project Overview

Technical details and design methodology.

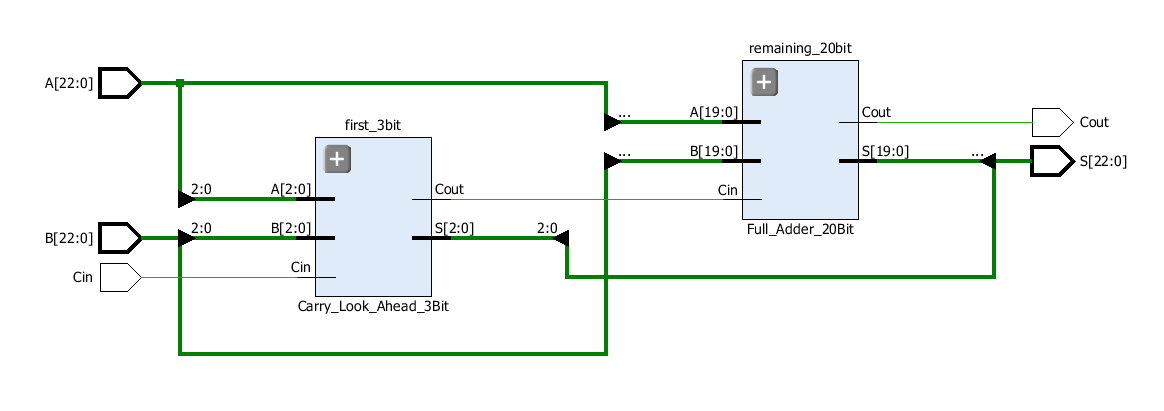

Hybrid RCA-CLA Design

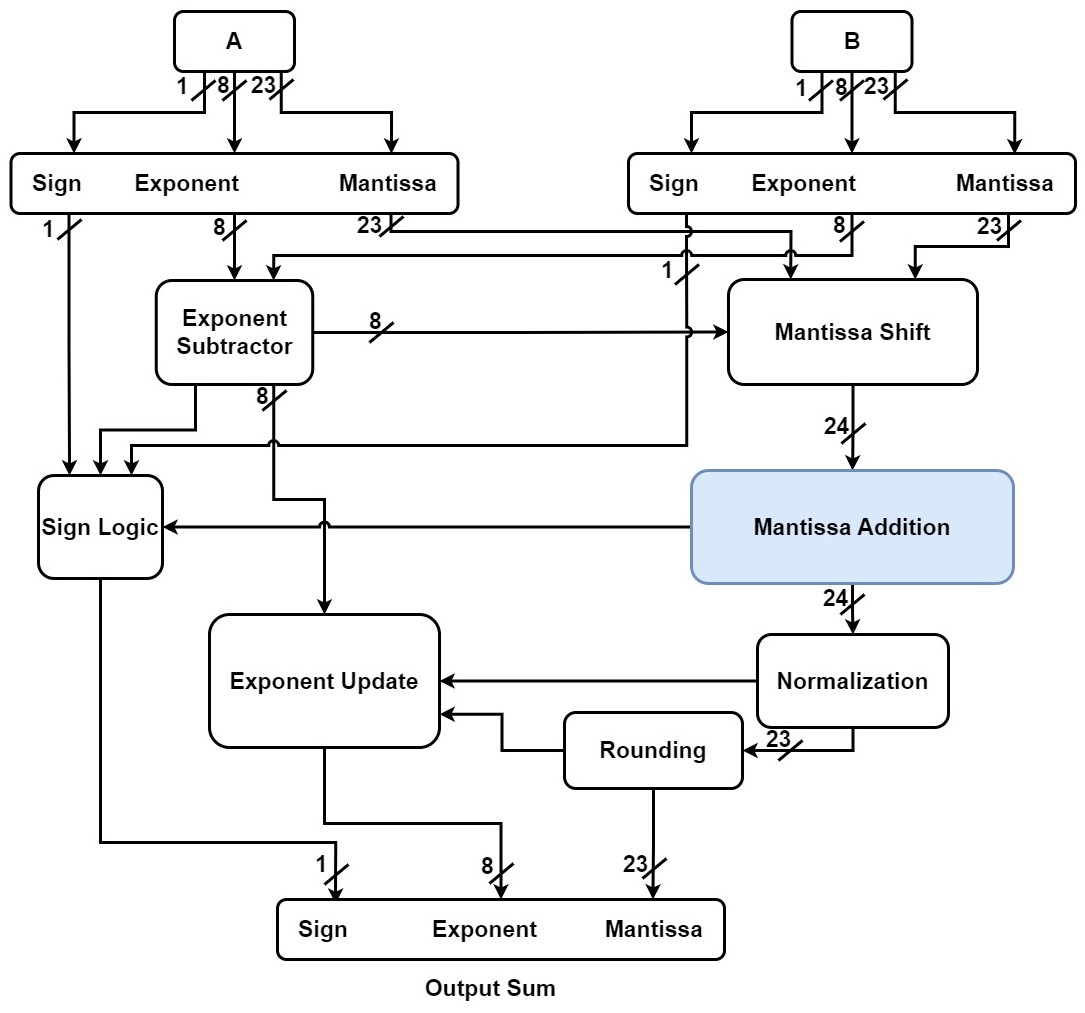

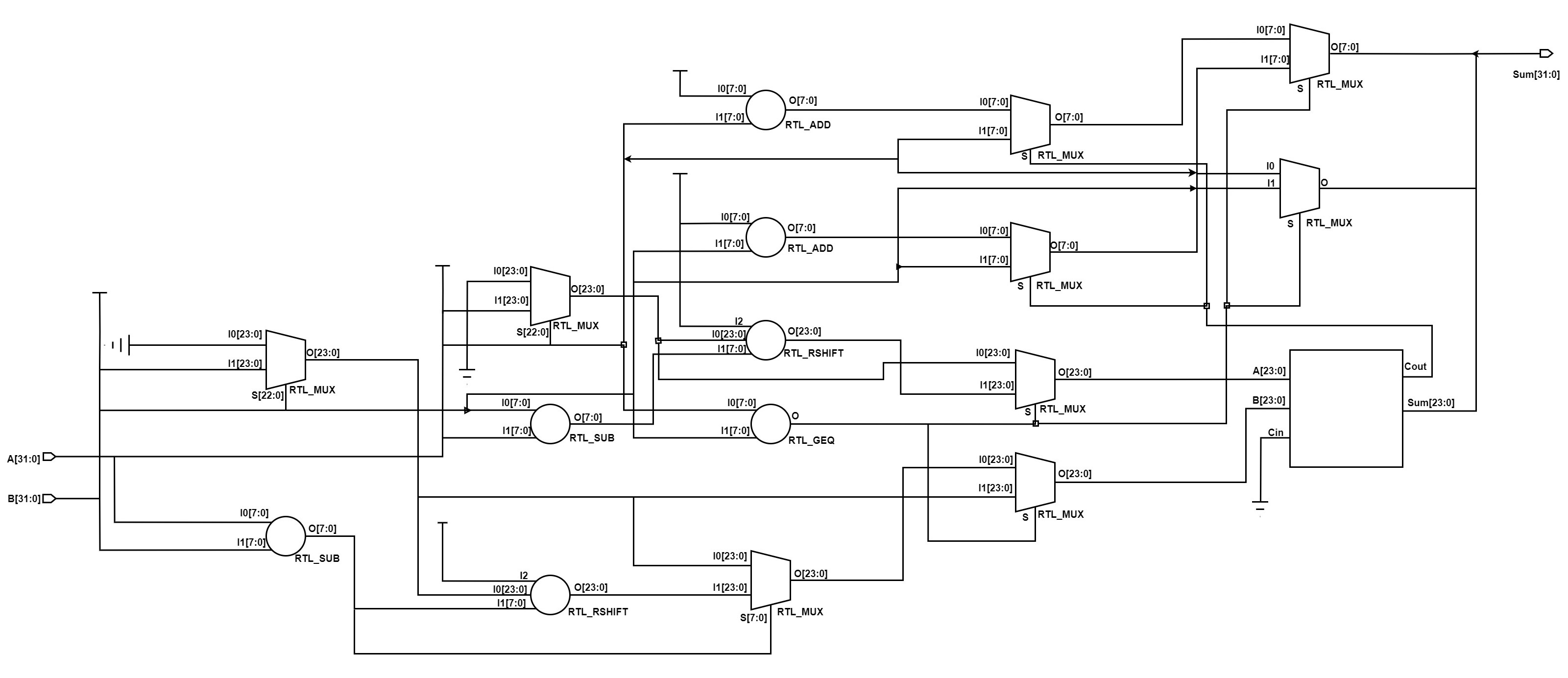

Floating-point addition is a critical operation in computer architecture but often incurs high costs in power, area, and delay. This project optimizes mantissa addition by implementing a hybrid approach that combines the simplicity of Ripple Carry Adders (RCA) with the speed of Carry Look-Ahead Adders (CLA). This hybrid design aims to balance performance and efficiency for Single Precision IEEE 754 floating-point operations.

Implementation Steps

- Decode IEEE 754: Extract sign, exponent, and mantissa; normalize mantissa with implicit bit.

- Align Exponents: Compare exponents and shift the smaller mantissa to align using a barrel shifter logic.

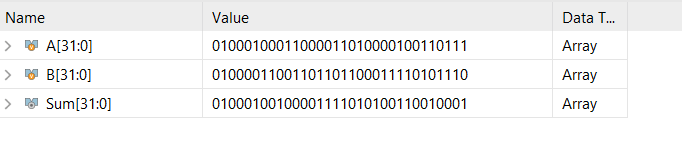

- Perform Addition: precise mantissa addition using the hybrid RCA-CLA adder handling sign and overflow.

- Normalize & Encode: Post-addition normalization, rounding, and re-encoding into standard IEEE 754 format.

Key Features

Project Info

- Category: VLSI Design

- Period: Aug 2022 - May 2023

- Project URL: GitHub Link